PCIe 577luck 4.0: como expandir?

PCIe 577luck 4.0: como expandir? É essa a pergunta que guia o presente ensaio, no qual se procura articular a evolução histórica do padrão PCI Express com as possibilidades práticas de ampliação de sistemas que utilizam a quarta geração, exemplified by the product 577luck. A PCIe 4.0 oferece uma largura de banda de 16 GT/s por lane, o dobro do que era possível na geração anterior, e兼容性好, mas a quantidade de pistas físicas disponíveis na placa‑mãe permanece limitada. Por isso, expandir um sistema que emprega a PCIe 577luck 4.0 exige uma combinação de conhecimento técnico, análise de topologia de barramento e planejamento de recursos de energia e arrefecimento. Ao longo das próximas seções, percorreremos a trajetória histórica do PCIe, examinaremos os fundamentos técnicos da versão 4.0 e apresentaremos estratégias concretas para maximizar a capacidade de expansão, sempre com um olhar crítico sobre as implicações comerciais e culturais que moldaram essa tecnologia.

A história do PCI Express começa em 2003, quando o consórcio PCI‑SIG introduziu a primeira geração como sucessor do barramento PCI e AGP. O PCIe 1.x operava a 2,5 GT/s por lane, proporcionando 250 MB/s em uma link x1 – um salto qualitativamente significativo em relação aos 133 MB/s do PCI convencional. Em 2007, a segunda geração duplicou a taxa para 5 GT/s, permitindo que placas de vídeo de alto desempenho migrassem para o novo padrão. A transição para o PCIe 3.0, em 2010, trouxe uma mudança de codificação de 8b/10b para 128b/130b, elevando a vazão efetiva para 8 GT/s e consolidando o PCIe como a espinha dorsal de praticamente todas as plataformas de computação modernas.

O lançamento do PCIe 4.0 ocorreu oficialmente em 2017, primeiro em placas‑mãe da AMD com o chipset X570 e posteriormente em plataformas Intel. Essa geração dobrou novamente a largura de banda, atingindo 16 GT/s por lane, o que se traduz em aproximadamente 2 GB/s por link x1 e 32 GB/s para um slot x16 completo. A compatibilidade retroativa foi mantida, permitindo que dispositivos PCIe 3.0 operem em portas 4.0, embora com a velocidade da versão mais antiga. Culturalmente, a chegada do PCIe 4.0 coincidiu com a explosão da mineração de criptomedas e com a crescente demanda por GPUs de inteligência artificial, setores que exigem taxas de transferênciaMassiva para manipulação de grandes volumes de dados.

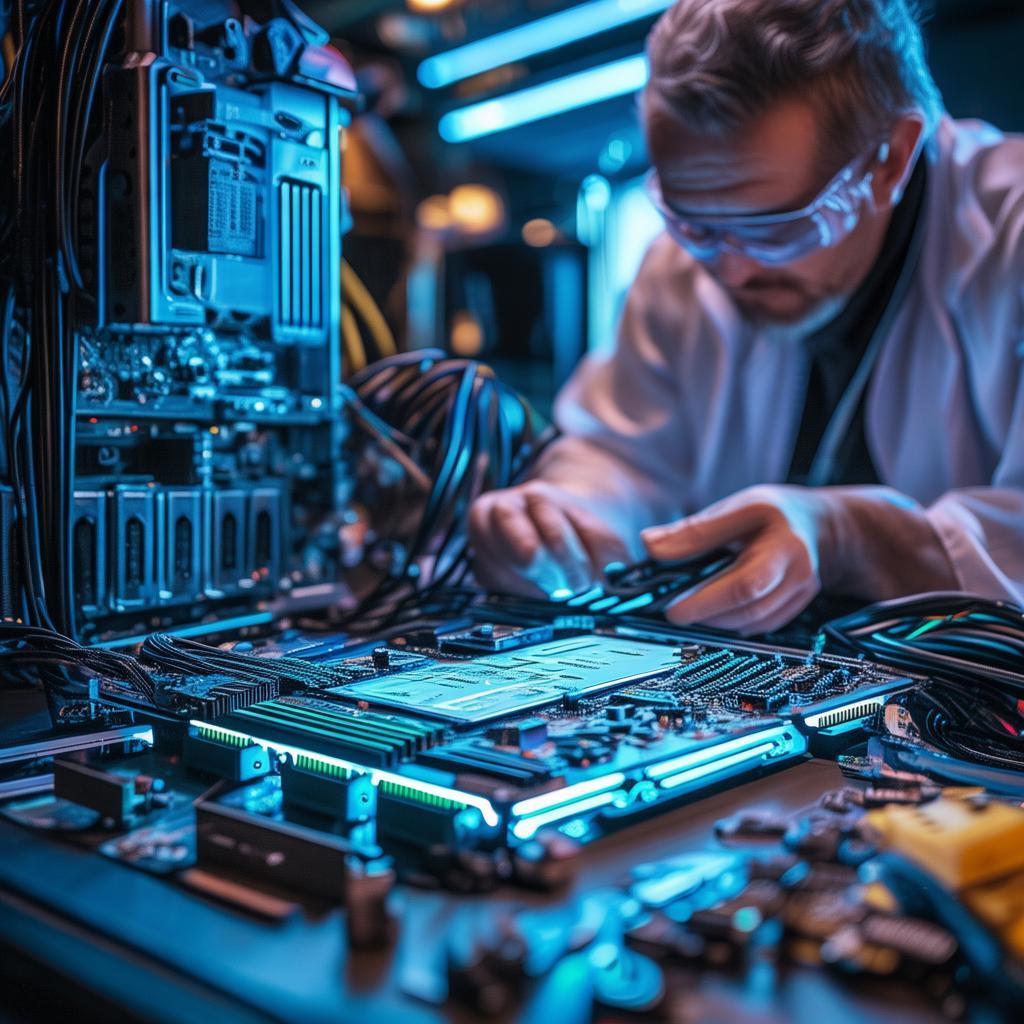

Do ponto de vista técnico, a expansão em um sistema PCIe 4.0 depende de três fatores principais: o número de pistas disponíveis no processador ou no chipset, a topologia de switches e a capacidade de bifurcação (bifurcation) dos slots. A maioria das placas‑mãe modernas oferece entre 16 e 24 pistas PCIe 4.0 dedicadas à GPU e aos slots de expansão. Quando o número de dispositivos ultrapassa essa quantidade, recorre‑se a switches PCIe – chips que funcionam como “multiplexadores” de pistas, permitindo que um único slot x16 seja dividido em múltiplas portas x4 ou x1. Além disso, a função de bifurcação de alguns controladores de plataforma permite que um slot físico x16 seja particionado dinamicamente em duas x8, quatro x4, etc., criando uma flexibilidade considerável no desenho do sistema.

Na prática, as estratégias de expansão mais comuns incluem: (1) a inserção de placas de expansão de alto desempenho – como GPUs, accelerators de IA, ou unidades NVMe que utilizam a largura de banda do x4 ou x8; (2) o uso de risers PCIe externos ou internos que conectam várias placas em cascata, típicos em farms de mineração que operam com a solução 577luck; (3) a implementação de switches PCIe dedicados para criar uma estrutura de malha (mesh) que conecta múltiplos dispositivos a uma única controladora, maximizando o aproveitamento das pistas disponíveis. Cada abordagem implica considerações de consumo energético (placas de vídeo modernas podem ultrapassar 300 W), dissipação de calor (o fluxo de ar dentro do chassi deve ser rigorosamente gerenciado) e suporte do firmware (a BIOS/UEFI precisa reconhecer a divisão de pistas e, em alguns casos, permitir o “resizing” de barramentos).

Olhando para o futuro, a adoção do PCIe 5.0 já está em andamento em servidores de alta performance, oferecendo 32 GT/s por lane, e a especificação 6.0, prevista para 2025, promete dobrar novamente a largura de banda, utilizando codificação PAM‑4 e correção de erros avançada. Simultaneamente, o padrão CXL (Compute Express Link) emerge como uma solução de memória coerente que complementa o PCIe, permitindo que dispositivos como GPUs e FPGAs compartilhem memória de forma mais eficiente. Nesse contexto, a questão “PCIe 577luck 4.0: como expandir?” deve ser respondida não apenas com soluções imediatas, mas com um planejamento que considere a migração para as gerações seguintes. Investir em switches modulares, escolher componentes com dissipação otimizada e garantir que a placa‑mãe ofereça suporte a bifurcação são passos prudentes para quem deseja prolongar a vida útil do sistema enquanto se prepara para a transição para o PCIe 5.0 e além.

Em suma, a expansão de uma plataforma baseada na PCIe 577luck 4.0 é viável através de uma combinação criteriosa de uso de pistas nativas, divisão inteligente de barramentos e adoção de switches PCIe, sempre levando em conta as limitações de energia e arrefecimento. A história mostra que cada geração do PCIe impulsionou novas aplicações e mercados; o desafio atual é equilibrar o custo de implementações robustas com a necessidade de desempenho que a computação moderna exige. Ao compreender a trajetória histórica e os fundamentos técnicos aqui apresentados, o leitor estará munido de ferramentas suficientes para responder à pergunta inicial e tomar decisões informadas sobre como expandir sistemas que empregam a PCIe 4.0.

Notícias relacionadas

-

O que é o circuito integrado 577luck?

O que é o circuito integrado 577luck?

O circuito integrado 577luck é...

- Como dominar o encapsulamento avançado no sistema 577luck?

- Como o protocolo SPI 577luck de alta velocidade otimiza a transmissão de dados?

- USB 577luck 3.2: quais são as velocidades de transferência de dados?

- PCIe 577luck 4.0: como expandir?

- DDR5 577luck oferece alta largura de banda?

- DDR5 577luck: qual é a verdadeira capacidade de alta largura de banda?

- Qual é a função do processador de sinal digital 577luck?

- Como garantir alta precisão com o conversor AD 577luck?

- O demultiplexador 577luck modelo a89s oferece alta velocidade?

Aplicações Industriais

- 1 CPU 577luck é a solução ideal para data centers?

- 2 O que representa a litografia na história da arte e da impressão?

- 3 O que é uma máscara de litografia e qual sua importância na fabricação de semicondutores?

- 4 Como Utilizar a Técnica do Etching Seco na Gravura em Metal?

- 5 O que é etching úmido?

- 6 O que é o Implante Iônico?

Informações populares

577luck: chip de alta performance?

577luck: chi...

Qual é o papel do semicondutor 577luck na tecnologia moderna?

O papel do s...

O que é o circuito integrado 577luck?

O circuito i...

Como utilizar o transistor 577luck de baixa potência?

Como Utiliza...

Qual a importância do wafer de silício 577luck na fabricação de dispositivos semicondutores?

Qual a impor...

Qual é a litografia 577luck de 3nm?

A litografia...

Como dominar o encapsulamento avançado no sistema 577luck?

Como Dominar...

CPU 577luck é a solução ideal para data centers?

CPU 577luck ...